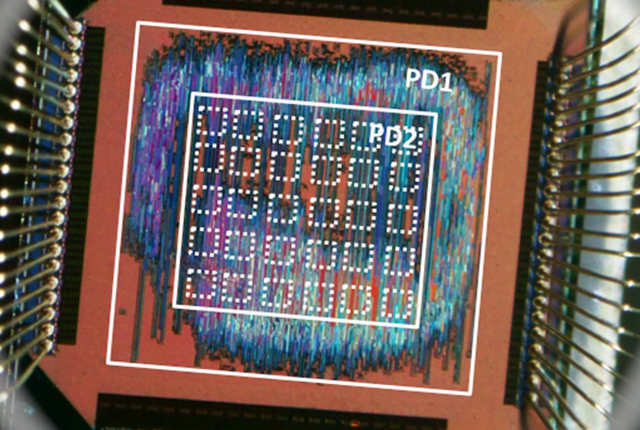

La industria de los microchips se revoluciona ante la salida de chips más pequeños y con más potencia cada año, y un factor común de la fabricación es la búsqueda de la perfección y de la exactitud de los procesos. Pero este modelo de construcción y trabajo, ¿es el más eficiente? Un grupo de investigadores de varias universidades del mundo coinciden en que no, en que ellos tienen un método 15 veces más eficiente que los chips convencionales utilizando chips “inexactos” que sacan provecho de los errores que cometen.

En 2003 un grupo de investigadores se reunió en torno a un proyecto que a sus cercanos dejó boquiabiertos: queremos hacer un chip que sea inexacto. Imaginamos respuestas como: ¿Qué? Hace 50 años nos devanamos los sesos intentando evitar la propagación de errores técnicos y humanos en el desarrollo de los chips y ustedes quieren hacer uno que directamente esté destinado a equivocarse. ¿Están locos? Al parecer los muchachos de la Universidad de California, la de Rice, la de Berkeley, la SNT de Singapur y el CEM de Suiza justificaron la internacional unificación de trabajo para crear su chip inexacto. Este cuenta con un sistema especial que le permite equivocarse para sacar más provecho y efectividad. Tanto como 15 veces más efectivo.

No se trata de otro intento frustrado por hacerme el gracioso, sino de un chip que al equivocarse por ser inexacto puede lograr –según sus responsables-, ser 15 veces más eficiente que los chips convencionales. Lo único que tiene que hacer para lograr este desafío es errar cálculos. Sí. Porque utiliza una técnica llamada “pruning” (traducible como “poda”), que consiste en permitir un tamaño menor de chips al eliminar alguno de sus componentes de uso irregular, además de permitirle a los que quedan que puedan cometer errores. La principal meta de estos chips inexactos es que usen sólo una fracción de energía eléctrica que usan los microprocesadores actuales, sin que los humanos podamos notar la diferencia en muchos aspectos.

El concepto es simple: Recortar el consumo de energía al permitir que los componentes de procesamiento -sumar y multiplicar números, en general- puedan cometer algunos errores. Al gestionar con inteligencia la probabilidad de errores y la limitación en la que los cálculos producen errores, los responsables descubrieron que al mismo tiempo puede reducir la demanda de energía e incrementar el rendimiento.

La idea es fantástica si la pensamos para actividades que soportan errores o que los tienen por inherencia, como el sonido y el video. Si el sistema puede manipularse y ser inteligente en la forma de “escoger” sus objetivos, podríamos tener 3 procesadores trabajando en conjunto y tener 1 que tenga un trabajo menos exacto para actividades menos exigentes. De esta manera, sacrificando un poco de funcionalidad en renderizado de imágenes o texto, por ejemplo en un móvil, la batería nos duraría un poco más. Según la fuente, estos chips pueden producir un 0.25% de errores en procesamiento, algo que no es perceptible al ojo humano en una imagen, por ejemplo, y esto ayudó a alcanzar niveles de eficiencia considerables sobre chips considerables. También podría ser útil para GPUs, pero sabremos más de ellos en 2013 cuando el proyecto esté finalizando su lanzamiento.

2 + 2 = 5 ? xD

#1 Pues si hablaras con un matematico de ciencias puras te diria que ese resultado es mas cercano al 4 😉 .Y recalco lo de Matematicas Puras 😉

Un Saludo

pues estos chips vendrian genial para los smatphones, ya que tienes que recargarlos todos los dias u_u

#2 Porque mejores baterias ni hablar ¿no?

El cerebro humano es así…

…O sea 2 + 2 = 3.99999… (0.o) ¡¡Qué loco!!

Muy interesante, puedo ver en sus comentarios que ponen la suma 2+2 con resultados como 5 o 3.9999, para el cerebro humano es casi instantáneo el 4, pero para una computadora una suma, resta, multiplicación o divicion es una adecuada combinación de compuertas "AND" , "OR" y "NOT".

Supongamos que queremos hacer una divicion, 560/5

si lo hacemos como en la primaria con el 560 dentro de la casita :

1) 5 cabe una vez en 5, llevamos 0 ;1

2) 5 cabe una vez en 6, llevamos 1 ;1

3) 5 cabe 2 veces en 10, llevamos 0;2

El resultado es 112, pero que tal si en ves de hacer 3 procesos solo hacemos 2, y lo dejamos en 110, el error es menor al 2% y nos ahorramos 33% del proceso.

Claro el tema no dice que esto exactamente sea como se comporten los chips que mencionan pero se entiende que al admitir cierto error la eficiencia aumenta.

Creo que esto sería muy útil implementado en el procesamiento 3D, ya que errores tan pequeños en una imagen con cientos de miles de poligonos no debieran notarse. Sin embargo aunque si bien en el procesamiento de imagenes y en el del sonido también funcionaría, la realidad dice que cualquier procesador actual del smartphone mas barato cumple sobradamente con dicha función sin un gasto de energia tan elevado (la mayor parte de la energía se gasta en la pantalla).

Quizas si lo saben enfocar bien podríamos estar en un par de años con unas buenas consolas 3D portátiles.

No se dejen deslumbrar por noticias de poca profundidad. Está tecnología existe hace muchas décadas se llama lógica difusa fuzzi logic Se basa en que electricamente es posible definir entre el apagado 0 y encendido 1 muchos otros valores esto podría tomarse cómo medio apagado o poco encendido. De allí lo de difuso. Esta comprobado que los computadores crecerian millomes de veces su capacidad, pero es complejo y sobretodo es un cambio de. Paradigma para la industria y para el hombre

#8 millomes de gracias por tu medio cerebro o poca inteligencia 🙂

si los procesadores pudieran diferenciar distintos niveles entre 0 y 1, estos ya no seria procesadores digitales sino analogicos… nada que ver con la noticia.

"Errar es humano"…y ahora también chipsino.

Ahora si se podràn hacer divisiones entre cero xD