Miniaturizar la fabricación de procesadores es la caldera que mantuvo caliente a la Ley de Moore durante todos estos años. A medida que nos acercamos al «dígito simple» en el conteo de nanómetros, surgen desafíos técnicos enormes, que obligan a repensar la mecánica actual del silicio. La gente de IBM, en asociación con la Universidad Estatal de New York, GlobalFoundries y Samsung, ha dado un paso enorme con su nuevo chip de 7 nanómetros, el primero en funcionar correctamente bajo esa tecnología.

El mejor método de fabricación al que podemos acceder hoy en un procesador es 14 nanómetros. Esto implica adquirir a un sistema con uno de los chips Broadwell de Intel, o los últimos Galaxy S6 de Samsung que poseen un SoC Exynos a esa escala. La sensación sobre las últimas «compresiones» es que los beneficios son cada vez menos marcados. Intel se ha enfocado más en reducir el consumo de energía que incrementar el rendimiento, una estrategia que para muchos usuarios simplemente no justifica reemplazar una plataforma completa. Aún así, las mejoras no se detienen. La Ley de Moore se ha convertido en sinónimo de Highlander, y no importa cuántas veces declaren su muerte, siempre encuentra la manera de resurgir.

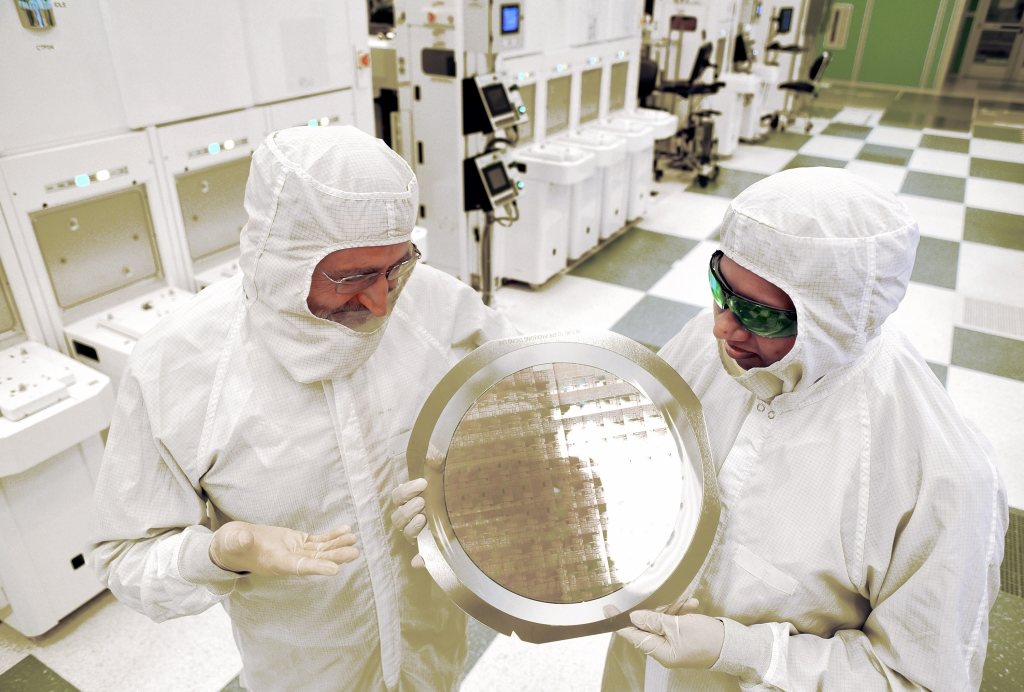

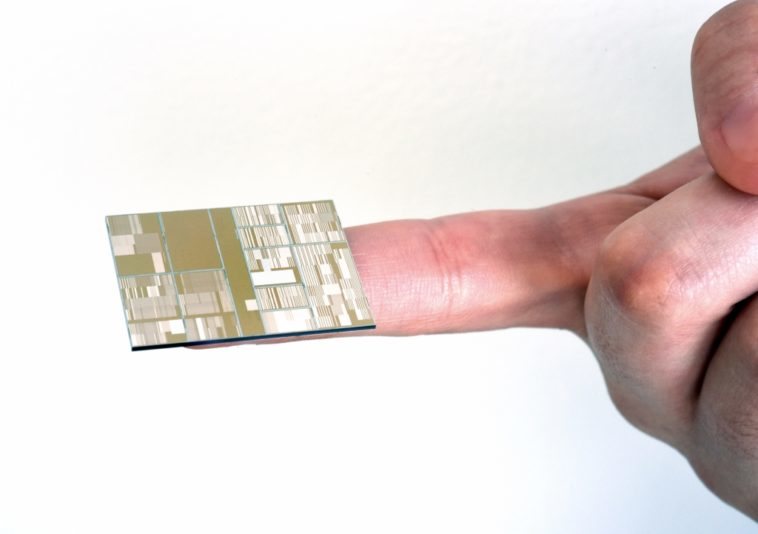

El nuevo salto evolutivo en la fabricación de chips llega gracias a IBM y la Universidad Estatal de New York, además de la alianza Common Platform que involucra a la gente de GlobalFoundries (compañía que «adquirió» la división de chips de IBM con 1.500 millones de dólares arriba), y a Samsung. Se trata de un prototipo de chip fabricado en 7 nanómetros, con transistores operacionales. Para perforar la barrera de los diez nanómetros, IBM debió implementar la llamada litografía EUV (Extreme UltraViolet), además de un canal formado por una aleación de silicio y germanio, reemplazando así al silicio puro. IBM anticipa que bajar de diez a siete nanómetros debería llevar a una reducción de superficie cercana al 50 por ciento, un parámetro que entusiasma al gigante azul y sus socios. La idea es lograr mejoras mínimas del 50 por ciento en la relación consumo-rendimiento, una vez que se hayan eliminado todos los bordes filosos del proceso.

Claro que, este último punto será bastante complicado. La aplicación de germanio ayuda a incrementar la movilidad de los electrones por debajo de diez nanómetros (o sea, su intervención no es negociable que digamos), y la litografía EUV aún es muy costosa. De hecho, si consideramos las palabras de Mukesh V. Khare, el número uno de IBM Research en procesos «sub-10nm», básicamente debemos esperar procesadores con un precio un poco más elevado, que justificarán el incremento a través de su rendimiento. De todas maneras, paciencia. Habrá que aguardar por lo menos hasta la segunda mitad de 2016 para ver a los 10 nanómetros en acción, un detalle que probablemente colocará a los 7 nanómetros en 2017 o 2018 si no surge ningún imprevisto.

2 Comments

Leave a Reply